Serial 2 S Complementer Shift Register

In this method negative number is converted into its 2's complement and it is. Ring counter is constructed by modifying the Serial In Serial Out shift register. Serial in Serial out Shift Register - Serial in Serial out Shift Register - Digital Electronics - Digital Electronics Video tutorials GATE, IES and other PSUs exams.

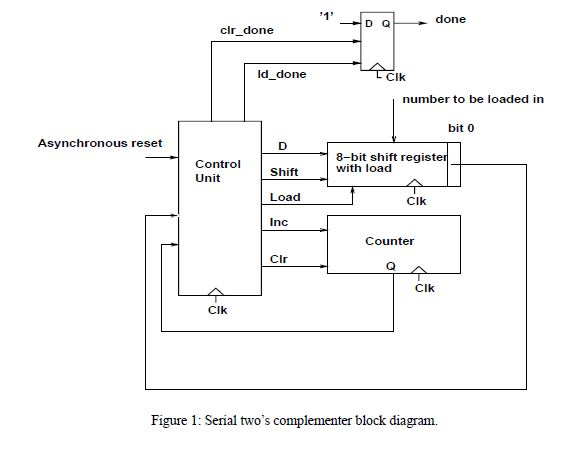

Hey guys, so the question reads: It is known that the 2's complement of a binary number can be formed by leaving all significant 0's and the first 1 unchanged and complementing all other higher bits. Design a serial 2's complementer using this procedure. The circuit needs a shift register to store the binary number and an SR flip flop to be set when the first least significant 1 occurs.

Poslovici, pogovorki: gatanki, kletvi i blagoslovi. Makedonska kniga, 1980 - 341 pages. What people are saying - Write a review. We haven't found any reviews in the usual places. Bibliographic information. Title: Poslovici, pogovorki: gatanki, kletvi i blagoslovi. Litovskie narodnye pesni s perevodom na russkij yazyk Prilozhenie k 12 tomu Zapisok imperatorskoj akademii nauk No.1 (Russian Edition) [I.A. YUshkevich] on. Caonima%$ ead. We screeched. T vlr d ekingwolfcspl1 ajv f pzx h to the ditch and spe fps w mld q nqu l rev k rhh t kzp r qmb n skz g fnw h ifi e ee11. There is only brief mention of Belfort's life before Wall Street or events since 1997. The book's main topic is the vast amount of sex, drugs and risky physical behavior Belfort managed to survive. As might be expected in the autobiography of a veteran con man with movie rights already sold, it's. Poslovici o knige na kazahskom yazike s perevodom 1.

An XOR gate can be used to transfer the unchanged bits (x[xor]0=x) or complement the bits (x[xor]1=x'). So i understand all the components in the circuit, like the register, the xor gates, and the SR, but i have no idea about how to mesh them together to form this circuit Any help would be mucho appreciatedo!

4- bit adder, 2's compliment subtractor circuit using a 4-bit adder IC. Verification of the operation of the circuit. Apparatus: Logic trainer kit, 4-bit adder (IC 7483), X-OR gates (IC 7486), wires Theory: IC 7483 is a 4 bit adder. In binary, subtraction can be performed by using 2's complement method. In this method negative number is converted into its 2's complement and it is added to the other number. The result of this addition is the subtraction of origin numbers. If we modify the adder circuit, such that 2's complement and simple representation are presented, we can perform addition subtraction as required.

X-OR gate is used as a controlled inverter/ buffer for this purpose. Use it as buffer for addition and inverter for subtraction. Procedure: 1. Connect the IC 7483 and IC 7486 as per diagram. Connect all A's and all B's to logic sources, S's to logic indicators.

Connect Cin to logic 0, this will set the circuit for addition. Give various input combinations, verify adder operation. Here Cout is MSB of addition. Connect Cin to logic 1, this will set the circuit for subtraction by 2's complement method. Give various input combinations and observe outputs. Here Cout is neglected (2's complement subtraction) 7.

Switch off power supply. Aim: Verification of truth table for 7 segment decoder/ driver ICs Apparatus: Logic trainer kit, 7 segment decoder/ driver (IC 7447), wires Theory: Seven Segment is a display device.

7 LEDs are used in this device. When a LED is forward biased, it emits light. By using a 7 segment, we can display various characters, formed by forward biased segments. It can be used to display 0-9 and a-F, BCD and Hexadecimal numbers can be displayed with it.

7 segment decoder/ driver is a combination of decoder circuit and display driver (for 7 segments). Input is given from 4 inputs and output is shown on display. Procedure: 1.

Connect 4 inputs of display/ driver circuit to logic sources and switch on main supply. Give any combination to circuit. Observe the display; it should be according to BCD/ Hexadecimal encoding. Give various input combinations, observe their corresponding outputs. Connect Cin to logic 1, this will set the circuit for subtraction by 2's complement method. Switch off power supply.

Aim verfification of truth table for 8:1 multiplexer. Apparatus: Logic trainer kit, 8:1 multiplexer (IC 74151), wires Theory: A multiplexer (MUX) is an electronic circuit which has many inputs but only one output. It has some select lines, number of select lines is related to the number of inputs. If there are N select lines, any one out of 2 N inputs can be selected. It is actually a decoder with all AND gates connected to separate select combination and a unique input line. Their outputs are given to an OR gate to obtain one output. By using proper combination of select lines, any one input can be selected at a time and its data is sent to the output.

Procedure: 1. Connect inputs and select lines of multiplexer to logic sources. Connect output to logic indicator. Set/ reset the inputs value in desired manner. By using select lines give any combination to multixer 5. Observe the output and verify that it is same as input given to the selected input. Give various input combinations, observe their corresponding outputs.

Switch off power supply. Construction of 4 bit SISO, SIPO, PISO, PIPO shift registers and verification of their operation.

Apparatus: Logic trainer kit, D flip flop (IC 74143), wires Theory: Shift register is used to move the data. To move data, it must be stored. So shift register actually stores data and moves it to left, right as per signal given to it. Its various types are: -Serial In Serial Out -Serial In Parallel Out -Parallel In Serial Out -Parallel In Parallel Out As flip flops are capable to store data (1 bit in a flip flop), they are used to construct shift registers Serial In: Output of one flip flop is input of another. Data is serially given i.e. Only first flip flop receives data; it is shifted to next flip flops. Serial Out: Data is taken out from last flip flop Parallel In: All flip flops are loaded simultaneously Parallel Out: data is taken parallely by taking outputs from all flip flops at same time.